# The Open University of Sri Lanka Faculty of Engineering Technology Department of Mechanical Engineering

Study Programme : Bachelor of Technology Honours in Engineering

Name of the Examination: Final Examination

Course Code and Title : DMX3304/ DMX3572/ MEX3272

**Applied Electronics**

Academic Year

: 2019/20

Date

: 11th October 2020

Time

: 1330hrs - 1630hrs

Duration

: 3 hours

WRITE YOUR REGISTRATION NUMBER CLEARLY WITHIN THE SPACE PROVIDED

#### **General Instructions**

- 1. Read all instructions carefully before answering the questions.

- 2. This question paper consists of Eight (8) questions in Eight (8) pages.

- 3. Answer any Five (5) questions only. All questions carry equal marks.

- 4. Answer for each question should commence from a new page.

- 5. This is a Closed Book Test (CBT).

- 6. Answers should be in clear hand writing.

- 7. Do not use Red color pen.

a) Briefly explain the Kirchhoff's Current Law (KCL) and Kirchhoff's Voltage Law (KVL).

[8 Marks]

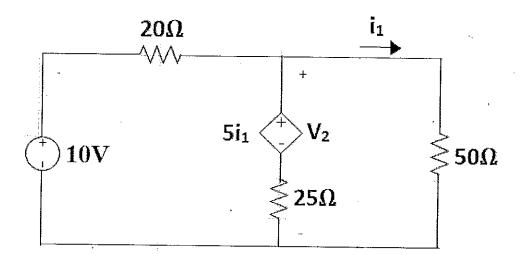

b) Consider the Circuit diagram given below in Figure Q01.

Figure Q01

- i. Find the equations for the voltage  $V_2$  and current  $i_1$  in the circuit given in the Figure Q01, using nodal analysis.

- ii. Solve the equations and find the values of V2 and i1.

[8 Marks]

[4 Marks]

### Question 02

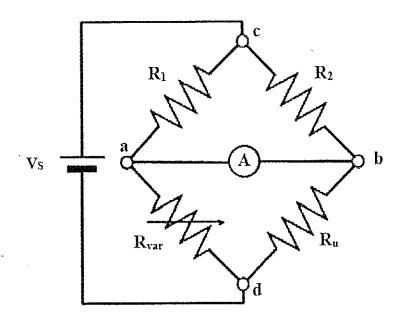

a) The circuit shown in Figure Q02(i), consists of two resistors  $R_1$  and  $R_2$  with resistances  $R_1 = 6 \Omega$  and  $R_2 = 1.5\Omega$ , one variable resistor  $R_{\text{var}}$ , one unknown resistor with value  $R_u$ , and a 9V battery connected.

When  $R_{\text{var}}$  is adjusted to  $12\Omega$ , there is zero current through the Ammeter. Find the unknown resistance  $R_{\text{u}}$ .

[10 Marks]

Figure Q02(i)

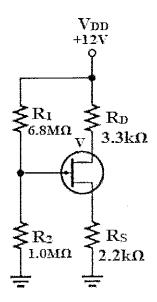

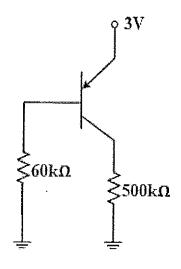

b) Determine  $I_D$  and  $V_{GS}$  for the JFET with voltage-divider bias shown in Figure Q02(ii). For this particular JFET, the internal parameters are such that  $V_D = 7V$ . (where, G-Gate, D-Drain, S-Source)

[10 Marks]

Figure Q02(ii)

a) Draw the output characteristics for a BJT (Bipolar Junction Transistor) in CE (Common Emitter) Configuration. Label each region clearly.

[5 Marks]

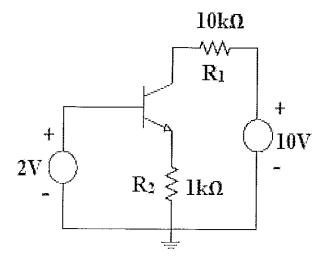

b) In the circuit shown in the Figure Q03(i), the BJT has a current gain ( $\beta$ ) of 50. If  $V_{EB}$  (Emitter – Base Voltage) is 600 mV, Find the  $V_{EC}$  (Emitter - Collector Voltage).

[7 Marks]

Figure Q03(i)

c) For a BJT circuit shown in Figure Q03(ii), assume that the 'β' of the transistor is very large and the V<sub>BE</sub> (Base – Emitter Voltage) is 0.7 V. Determine the mode of operation of the BJT.

[8 Marks]

Figure Q03(ii)

a) Briefly explain 4 characteristics of an ideal Op-amp.

[4 Marks]

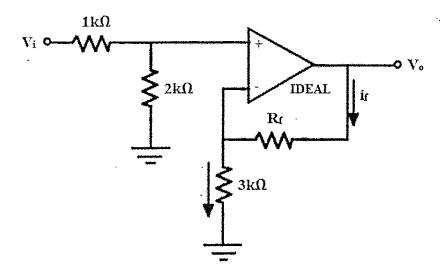

b) For the ideal Op-amp shown in Figure Q04(i), Find the value of resistor R<sub>f</sub> to obtain a gain of 5.

[6 Marks]

Figure Q04(i)

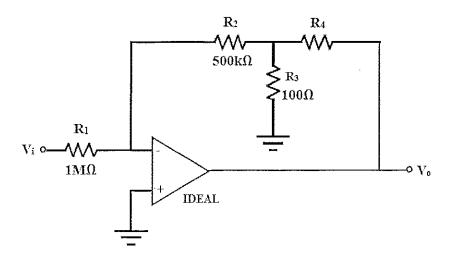

c) Evaluate the following amplifier circuit given in Figure Q04(ii), and Determine the value of resistor R<sub>4</sub> in order to obtain a voltage gain (V<sub>0</sub>/V<sub>i</sub>) of (-120).

[10 Marks]

Figure Q04(ii)

a) Draw circuit symbols of a diode and a Zener diode. Sketch the V/I characteristics of diode and Zener diode.

[4 Marks]

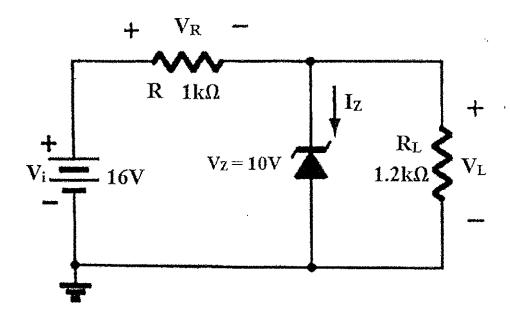

b) For the Zener diode regulator shown in Figure Q05(i), determine V<sub>L</sub>, V<sub>R</sub> and I<sub>Z</sub>. [5 Marks]

Figure Q05(i)

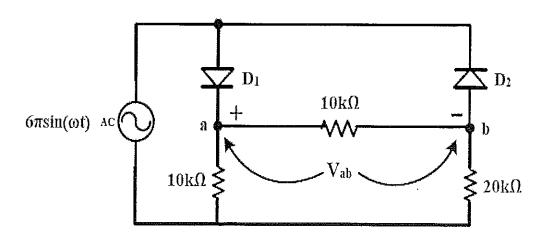

c) In the circuit shown in Figure Q05(ii), assume that the diodes  $D_1$  and  $D_2$  are Ideal. Find the average value of voltage  $V_{ab}$  (in volts) across terminals 'a' and 'b'.

[11 Marks] -

Figure Q05(ii)

a) What are the main advantages of Hexadecimal numbering system?

[3 Marks]

b) Convert the number 3543216 (Hexadecimal) to Decimal number.

[4 Marks]

c) Determine the addition of the following numbers.

[4 Marks]

- i. 00111001<sub>2</sub> to 00101001<sub>2</sub>

- ii. 10101.101<sub>2</sub> to 1101.011<sub>2</sub>

- d) Determine the multiplication of 1010<sub>2</sub> by 1011<sub>2</sub>.

[4 Marks]

e) Determine the division of 11100110<sub>2</sub> by 110<sub>2</sub>. State the quotient and remainder clearly. [5 Marks]

#### Question 07

a) State the De' Morgan's theorem.

[4 Marks]

b) Prove the following Boolean Identities.

i.

$$A \overline{B} C + A B C + A B \overline{C} = A (B + C)$$

[4 Marks]

ii.  $A C + B \overline{C} = A B C + \overline{A} B \overline{C} + A B \overline{C} + A \overline{B} C$  [4 Marks]

c) The K-map for a Boolean function is shown in Figure Q07(i), Find number of essential prime implicants for this function.

[4 Marks]

| CD AB | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 1  | 1  | 0  | 1  |

| 01    | 0  | 0  | 0  | 1  |

| 11    | 1  | 0  | 0  | 0  |

| 10    | 1  | 0  | 0  | 1  |

Figure Q07(i)

d) Use the K-Map technique and minimize the Boolean expression,

$$Y = \overline{A} \, \overline{B} \, \overline{C} \, D + \overline{A} \, B \, C \, \overline{D} + A \, \overline{B} \, \overline{C} \, D + A \, B \, \overline{C} \, \overline{D}$$

[4 Marks]

### Question 08

a) Draw the symbols of the four Logic gates AND, OR, NAND and NOR for two inputs A and B.

[3 Marks]

b) Consider the Boolean function,

$$Z = A \overline{B} C$$

Find the minimum number of 2 input NAND gates required to implement the function above, assuming the inputs A, B, and C are available. (Hint: Draw the Logic gate diagram).

[4 Marks]

c) Consider the Boolean Expression,

$$X = AB + ABC + A\overline{B}\overline{C} + A\overline{C}$$

i. Draw the logic diagram for the expression.

[2 Marks]

ii. Minimize the expression.

[2 Marks]

iii. Draw the logic diagram for the reduced expression.

[2 Marks]

d) Prove the following expression by use of a truth table.

$$\overline{A} B \overline{C} + \overline{A} B C + \overline{A} \overline{B} C = \overline{A} B + \overline{A} C$$

[7 Marks]

**END**