# The Open University of Sri Lanka Faculty of Engineering Technology Department of Mechanical Engineering

Study Programme

: Bachelor of Technology Honours in Engineering

Name of the Examination: Final Examination

Course Code and Title : DMX3304 Applied Electronics

Academic Year

: 2020/21

Date

: 09th February 2022

Time

: 1400hr - 1700hr

Duration

: 3 hours

## **General Instructions**

- 1. Read all instructions carefully before answering the questions.

- 2. This question paper consists of Eight (8) questions in Eight (8) pages.

- 3. Answer any Five (5) questions only. All questions carry equal marks.

- 4. Answer for each question should commence from a new page.

- 5. This is a Closed Book Test (CBT).

- 6. Answers should be in clear handwriting.

- 7. Do not use Red color pen.

a) Briefly explain the definition of Circuit analysis. State the two main methods of analyzing an electrical circuit.

[5 Marks]

b) State and explain the Kirchhoff's Current Law (KCL).

[3 Marks]

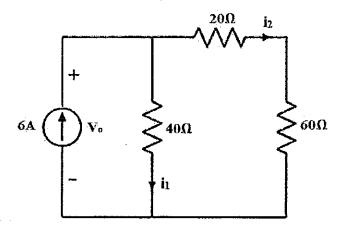

- c) Consider the circuit given below in Figure Q01, use KCL, KVL, and Ohm's Law to:

- i. Find i1, i2, and Vo.

[6 Marks]

ii. Check the power balance in this circuit.

[6 Marks]

Figure Q01

## Question 02

a) State three advantages of the Wheatstone bridge method.

[3 Marks]

b) State three disadvantages of a Field Effect Transistor (FET) over that of a Bipolar Junction Transistor (BJT).

[3 Marks]

a) State the three modes of the operation of Bipolar Junction Transistors (BJT). Briefly explain how to force a BJT to operate in each of the three modes.

[5 Marks]

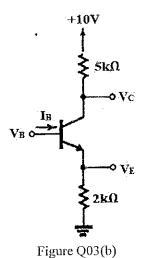

- b) Consider the Bipolar Junction Transistor (BJT) given in the circuit in Figure Q03(b) where  $\beta = 50$ . If  $V_{CEsat} = 0.3V$  and  $V_{BE} = 0.7V$ ,

- i. Find the  $V_{CE}$  and the Operating mode of the BJT transistor (i.e., whether forward active, saturation, or cutoff), when  $V_B = 5V$ .

[6 Marks]

ii. Find  $V_E$ ,  $V_C$ , and  $I_B$  when  $V_B = 2.5V$ .

[3 Marks]

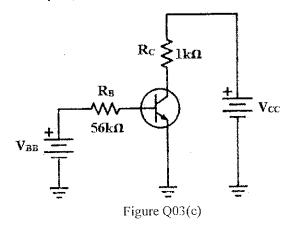

c) Consider the NPN Bipolar junction transistor (BJT) circuit shown in Figure Q03(c). A base current of  $50\mu A$  is applied to the transistor and a voltage of 5V is doped across the R<sub>C</sub>. Determine the  $\beta_{DC}$  (DC current gain) of the transistor.

[6 Marks]

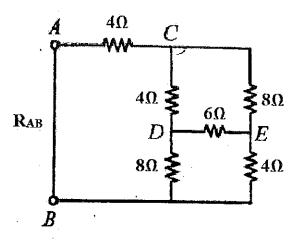

c) Consider the circuit given below in Figure Q02(c). Calculate the input resistance of the circuit between the points A and B (R<sub>AB</sub>).

Figure Q02(c)

[7 Marks]

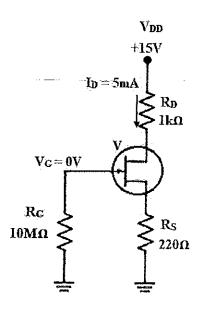

d) Consider the Field-Effect Transistor (FET) amplifier with DC voltage ( $V_{DD}$ ) given below in Figure Q02(d). Determine the values of  $V_{DS}$  and  $V_{GS}$ .

Figure Q02(d)

[7 Marks]

a) State four characteristics of a Non-Ideal Op-amp.

[4 Marks]

b) State three applications of using Operational Amplifiers.

[3 Marks]

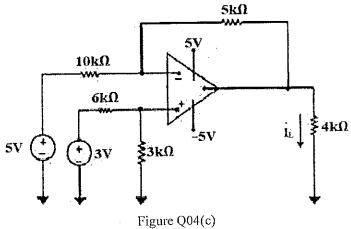

c) Consider the Ideal Op-amp shown in Figure Q04(c). Calculate the value of the current  $i_{\rm L}$ .

[6 Marks]

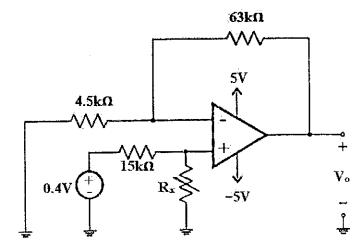

d) Consider the following Ideal Op-amp circuit given below in Figure Q04(d).

i. Determine the Output voltage  $V_0$  if  $R_x = 60k\Omega$ .

. . [3 Marks]

ii. Calculate the the largest value possible for  $\mathbf{R}_{x}$  before the amplifier saturates.

[4 Marks]

Figure Q04(d)

a) State four advantages of using Zener diodes.

[4 Marks]

b) Briefly explain the definition of an Ideal diode. Sketch the I-V characteristics curve of an ideal diode.

[4 Marks]

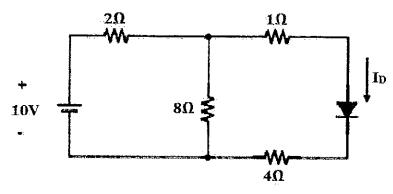

- c) Consider the diode circuit shown in Figure Q05(c). Find the diode current I<sub>D</sub> by using each of the following methods.

- i. Ideal diode model

[3 Marks]

ii. Offset diode model with  $V_{\gamma} = 0.7 \text{ V}$

[3 Marks]

Figure Q05(c)

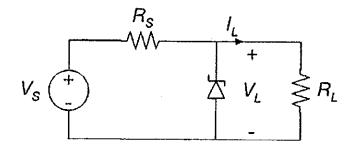

- d) Consider the Zener diode voltage regulator shown in Figure Q05(d). The Zener diode is characterized by  $V_Z = 3.3V$  and  $R_Z = 10\Omega$ . For this circuit  $V_S = 5V$ ,  $R_S = 250\Omega$  and the load resistance  $R_L = 1k\Omega$ .

- i. Calculate the voltage V<sub>L</sub> across the load R<sub>L</sub>.

[2 Marks]

ii. Calculate the power dissipated in the load.

[2 Marks]

iii. Calculate the power dissipated in the Zener diode.

[2 Marks]

Figure Q05(d)

a) State what is meant by the Binary number system.

[2 Marks]

b) List the advantages of the Octal number system over the binary system.

[2 Marks]

c) Convert the Hexadecimal number 5A.B16 to an Octal number.

[3 Marks]

d) Convert the Binary number 110101112 to Decimal, Octal, and Hexadecimal number systems.

[4 Marks]

e) Perform Binary addition and subtraction on the following unsigned binary numbers.

i. 1111<sub>2</sub>+1001<sub>2</sub>

[2 Marks]

ii.  $11001_2 - 1111_2$

[2 Marks]

f) Represent the Decimal number -14<sub>10</sub> as an 8-bit Binary number using 2's Complement representation.

[5 Marks]

## Question 07

a) Briefly explain the definition of Universal gates in Boolean algebra. List the two types of Universal gates.

[3 Marks]

b) Draw the Logic circuit for the **EXOR** gate for two inputs A and B, state the Boolean function and construct the truth table.

[3 Marks]

c) Reduce the following Boolean expression to ONE literal.

$$\bar{A}B(\bar{D}+\bar{C}D)+B(A+\bar{A}CD)$$

[4 Marks]

d) Draw the Logic diagram corresponding to the following Boolean expression without simplifying.

$$(A+B)(C+D)(\bar{A}+B+D)$$

[4 Marks]

e) Construct the Truth table for the following function and express the function as a **Sum** of Min terms (SOP).

$$f = (XY + Z)(Y + XZ)$$

[6 Marks]

## **Question 08**

a) State two advantages of using Karnaugh Maps (K-Maps) as a Boolean algebraic simplification technique.

[2 Marks]

b) Implement the following expression with a 3-Level **NAND circuit**. (Hint: Simplify the expression and use only NAND gates to implement the circuit).

$$F = A\overline{B} + ABD + AB\overline{D} + \overline{A}\overline{C}\overline{D} + \overline{A}B\overline{C}$$

[4 Marks]

c) Simplify the following expression using a 3-Variable K-Map.

$$f = (\bar{X}\bar{Y} + YZ + \bar{X}Y\bar{Z})$$

[4 Marks]

d) Determine the **Min terms** of the following Boolean expression by plotting the function in a **K-Map**.

$$F = \vec{C}D + AB\vec{C} + AB\vec{D} + \vec{A}\vec{B}D$$

[5 Marks]

f) Simplify the following Boolean function using a 3 Variable K-Map and express the function as a Product of Sums (POS).

$$F = \bar{X}\bar{Z} + \bar{Y}\bar{Z} + Y\bar{Z} + XY$$

[5 Marks]

**END**