The Open University of Sri Lanka Department of Electrical and Computer Engineering Bachelor of Technology - Level 05

## ECX5231 - Network Theory

Final Examination 2007/2008

Duration: 3 hours

Date: 06.05.2007

Time: 13.30-16.30

This question paper consist of two sections over three pages. The paper contains eight questions and all questions carry equal marks. Selecting any question from section B.

Section A

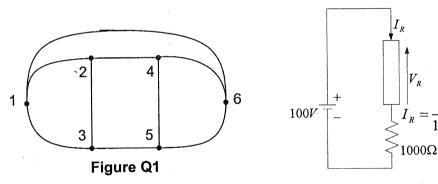

- O1 Structure of an electrical circuit is shown in the figure Q1.

- (a) Show the structure of the nodal admittance matrix  $Y_N$  of the circuit given in figure Q1, if the all branches contain passive elements and independent sources. i.e. show all non zero elements as a  $_{m,n}$ .

- (b) Branch d contain a Voltage Controlled Voltage Source (VCVS) of strength  $\mu$  which is driven by the voltage across the branch c. Derive the stamp of the given voltage controlled voltage source (VCVS).

- (c) Suggest a representation which facilitates to the exploitation of sparcity. Represent the nodal admittance matrix found in Q1 (a) using the suggested method.

- (d) Show two steps of a reordering process that used to preserve the sparcity.

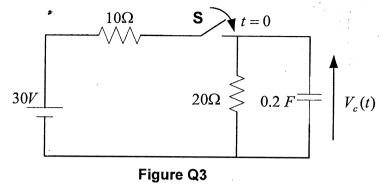

Figure Q2

- Q2 A simple non linear circuit is shown in the figure Q2

- (a) Represents the given circuit using the companion network model of the non linear element.

- (b) Obtain a formulation for the voltage V<sub>R</sub>.

- (c) Find the current through the non-linear resistor applying Newton-Rapson method. For initial guess take  $V_R = 20 \text{ V}$  and do at least 3 iterations.

Q3 It is required to perform a transient analysis of the simple first order RC circuit shown in the Figure Q3. Assume that the capacitor is initially charged to 10 V and the switch is closed at t=0.

- (a) Represents the given circuit by replacing the capacitor with its companion network model using the backward Euler algorithm.

- (b) Formulate the model of the given circuit to obtain the transient solution.

- (c) Determine the voltage across the capacitor at t=0.3s, 0.6s, and 0.9s if the initial voltage across the capacitor is 10 V. (take time  $\Delta T$  as 0.3s)

- (d) Briefly explain how the trade off among the stability, accuracy, and computational effort is achieved in the simulation of electrical circuits.

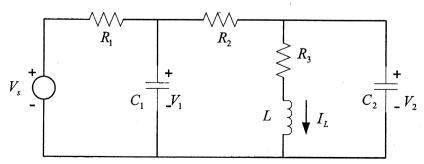

- Q4 A dynamic circuit is shown in the figure Q4. The circuit is exited by the source  $V_s$  and output is taken from  $V_2$ .

- (a) Derive the state space model of the circuit

- (b) Obtain the transfer function of the circuit using the state space model

- (c) List the types of analysis that can be carried with the help of state space models of an electric circuit.

- (d) Sketch an algorithm to show how to generate the state space model by assuring the minimal number of equations of a dynamic electrical circuit.

Figure Q4

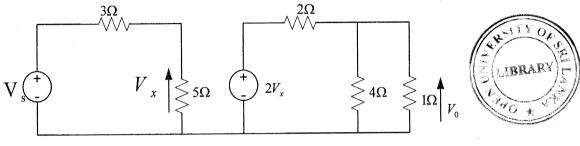

- Q5 An electrical circuit having a voltage controlled voltage source is shown in figure Q5. The strength of the controlled source is  $\beta$ .

- (a) Obtain the adjoint network model of the voltage controlled voltage source (VCVS) using Tellegen's theorem.

- (b) Derive an expression for  $\frac{\partial V_o}{\partial \beta}$ .

- (c) Find the sensitivity of the V<sub>0</sub> for all parameters of the circuit.

- (d) List the advantages of using adjoint network method for sensitivity analysis of electrical circuits.

Figure Q5

## Section B

A simulator has to be developed for the DC bias point analysis and sensitivity analysis of circuits having linear and non linear components. Simulator may have to be performing number of pre tasks before formulation of the circuit. Some post processing also has to be performed to display the results of the above four types of analysis.

- Q6 Draw a detailed functional block diagram of the simulator by indicating the following. Label each module showing whether t is used for particular type of analysis only or is a shared module

- (a) Core functions of the simulation process.

- (b) Pre tasks of the simulation and post processing after the simulation

- Q7 Suggest at least two techniques that can be used to optimize the use of resources during simulation (other than the sharing of resources) and briefly explain them.

- Q8 If it is required to integrate the small signal analysis to this module,

- (a) Describe how some modules of the above system can be used for produce some intermediate results for this purpose.

- (b) Briefly explain how the remaining tasks can be performed.