The Open University of Sri Lanka

Department of Electrical and Computer Engineering

Final Examination –2010

ECX 4230 – Fault Diagnosis in Electronic Circuits

(Closed Book)

Time: 1400-1700hrs.

Date: 21,03,2011

## Answer any five questions.

1. (a) (i) A npn transistor is tested using an analog multimeter set to  $x10\Omega$  range. Indicate the meter response in the following table as 'low  $\Omega$ ', 'high  $\Omega$ ' and 'zero  $\Omega$ '.

| Black probe | Red probe | Response |

|-------------|-----------|----------|

| base        | emitter   |          |

| base        | collector |          |

| emitter     | base      |          |

| collector   | base      |          |

| collector   | emitter   |          |

| emitter     | collector |          |

- (ii) State the failure modes of a transistor.

- (b) The data of a triac is given below.

| Repetitive peak off state voltage | = 400  V  |

|-----------------------------------|-----------|

| On state current RMS              | = 8 A     |

| Peak gate voltage                 | = 10  V   |

| Peak gate current                 | = 2 A     |

| Min. gate trigger current         | = 60  mA  |

| Min. gate trigger voltage         | = 2 V     |

| Peak on-state voltage             | = 1.55  V |

| Holding current                   | = 6  mA   |

| Latching current                  | = 75  mA  |

|                                   |           |

- (i) Briefly describe these data statements.

- (ii) State the four triggering modes of a triac.

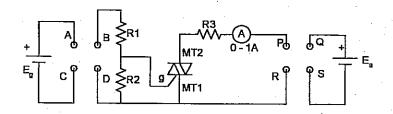

- (iii) The circuit shown in Figure-Q1 is used to test a suspected triac having the above data. Find suitable values for E<sub>g</sub>, E<sub>a</sub>, R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub>. State the steps you will follow to test the triac and the observations expected. The points A, B, C, D, P, Q, R and S are connector terminals.

Figure - Q1

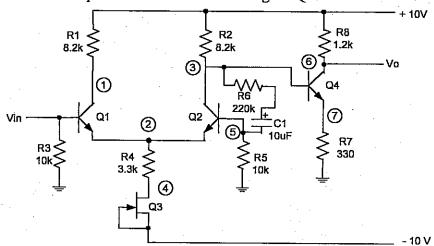

2. A differential amplifier circuit is shown in Figure-Q2.

Figure - Q2

The transistors Q1, Q2 and Q4 are of high gain and Q1 and Q2 are matched. The transistor Q3 is an n-channel JFET in which  $I_D = 0.125(V_{GS}-V_P)^2$ , where  $V_P = -4V$ . You may assume usual notation.

- (i) Calculate the test point voltages at no signal. (Do not assume a value for test point 6.)

- (ii) A signal of 1 kHz, 40mV peak to peak is given to the input and the resulting waveforms at the test points are observed using an oscilloscope. Draw the waveforms observed at the test points 3 and 6 to a common time scale with the input for the following settings.

- (a) When the vertical amplifier of the scope is dc coupled.

- (b) When the vertical amplifier of the scope is ac coupled.

- (iii) Following table shows test point voltages under fault conditions. Identify the faulty component/s with fault type giving reasons.

| case | 1     | 2     | 3     | 4     | 5 | 6     | 7    |

|------|-------|-------|-------|-------|---|-------|------|

| A    | 10.00 | 0     | 10.00 | 0     | 0 | 2.23  | 2.13 |

| В    | -0.50 | -0.60 | 2.96  | -7.20 | 0 | 2.46  | 2.36 |

| С    | 1.80  | -0.60 | 1.80  | -7.20 | 0 | 1.50  | 1.20 |

| D    | 1.80  | -0.60 | 1.80  | -7.20 | 0 | 10.00 | 0    |

3. (a) After repairing a DC power supply, what are the parameters you should check to confirm its correct operation?

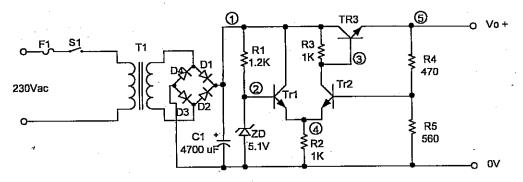

Figure -Q3

- (b) The circuit of a dc power supply is shown in Figure-Q3. Assume the voltage at test point 1 lies between 12V to 15V.

- (i) Calculate the output voltage.

- (ii) Show a method to obtain any voltage between 5V to 10V.

- (iii) Show a modification to implement a current limit for this circuit if the maximum load current is 2A.

- (iv) The table below shows the voltages at test points under fault conditions. Find the faulty component/s and fault type giving reasons.

| case | 1    | 2   | 3    | 4   | 5    |

|------|------|-----|------|-----|------|

| A    | 15.0 | 5.1 | 14.7 | 4.5 | 14.0 |

| В    | 15.0 | 5.1 | 15.0 | 4.5 | 0    |

| С    | 15.0 | 5.1 | 5.7  | 4.5 | 5.1  |

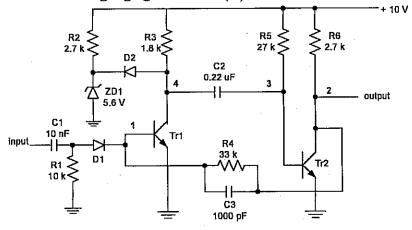

4. Consider the multivibrator circuit shown in Figure-Q4. The transistors may be assumed as having high gain and  $V_{CE(sat)} = 0$ .

Figure - Q4

- (i) Identify the type of this multivibrator. Calculate the test point voltages when there is no input signal and find the collector current in each transistor.

- (ii) A pulse of short duration having an amplitude of 8V is applied to the input. Draw the resulting waveforms at each test point on a common time scale. Calculate and mark important voltage and time values on your sketch.

- (iii) Under fault conditions, all test point voltages are observed before applying any input. Then the test points are observed by an oscilloscope after applying a narrow test pulse of 8V. Some of the results observed are listed below. Find the faulty component/s indicating the fault type with reasons.

| case | 1   | 2   | 3   | 4   | other                           |

|------|-----|-----|-----|-----|---------------------------------|

| A    | 0.0 | 0.0 | 0.6 | 0.6 | no output                       |

| В    | 0.0 | 0.0 | 0.6 | 6.2 | no output pulse; -ve pulse at 3 |

| С    | 0.0 | 0.0 | 0.6 | 6.2 | output pulse width > normal     |

| D    | 0.0 | 0.0 | 0.6 | 6.2 | output pulse height< normal     |

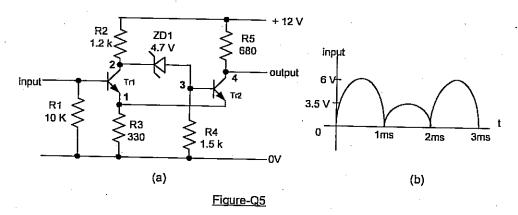

5. A Schmitt trigger circuit is shown in Figure-Q5. Assume the transistors have high gain and  $V_{CE(sat)} = 0$ .

- (i) Calculate the input threshold voltages and hysteresis of this circuit.

- (ii) Find the possible values that the output can have and derive the test point voltages for these cases.

- (iii) Sketch the waveform of the output when the signal shown in Figure-Q5(b) is applied to the input. Your sketch must show the input and the output on a common time scale and the time and voltage values must be marked clearly.

- (iv) Under fault conditions, two dc voltages are given to the input and the resulting test point voltages are listed below. State the faulty component/s giving fault type with reasons.

| case | input | 1    | 2    | 3    | 4    |

|------|-------|------|------|------|------|

| _A_  | 0.00  | 0.00 | 12.0 | 0.00 | 12.0 |

| В    | 0.00  | 0.00 | 8.16 | 4.06 | 12.0 |

| С    | 6.00  | 5.40 | 8.16 | 4.06 | 12.0 |

| D    | 6.00  | 5.40 | 5.60 | 0.90 | 0.00 |

- 6. (a) State the sections necessary for a circuit to act as an oscillator.

- (b) State the factors that will cause frequency instability in oscillators. What are the steps that can be used to overcome these effects?

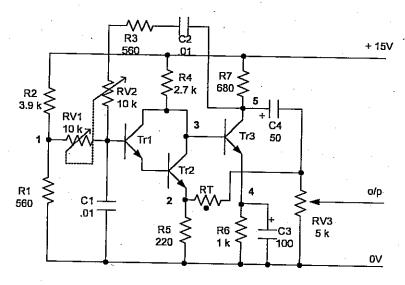

- (c) The circuit of a Wien bridge oscillator producing sine wave output is shown in Figure-Q6. The transistors Tr1, Tr2 and Tr3 are of high gain type and RT is a thermistor.

Figure - Q6

- (i) Identify the components which determine the output frequency. What is the phase relationship of the signal at 5 with the signal at the base of Tr1? Also state the function of RT.

- (ii) Estimate the frequency range of this oscillator.

- (iii) Calculate the dc voltages of the test points.

- (iv) Following table shows the dc voltages at test points under faulty conditions. Identify the faulty component/s indicating reasons to support your answers.

| fault | 1   | 2   | 3   | 4   | 5    | output      |

|-------|-----|-----|-----|-----|------|-------------|

| Α     | 1.9 | 0   | 9.5 | 8.9 | 9.0  | No output   |

| В     | 1.9 | 0.7 | 6.7 | 6.5 | 15.0 | -do         |

| C     | 0   | 0   | 9.5 | 8.9 | 9.0  | -do         |

| D     | 1.9 | 0.7 | 6.6 | 6.0 | 10.9 | Square wave |

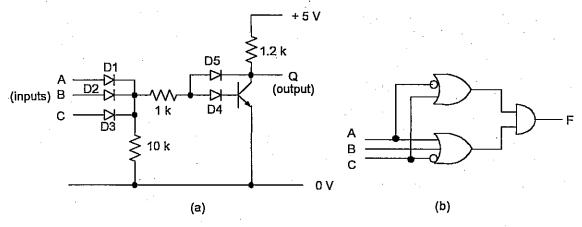

7. Two logic circuits are shown in Figure – Q7.

Figure - Q7

- (a) For the circuit shown in Figure-Q7(a).

- (i) Give the truth table of this circuit.

- (ii) State the logic function of this circuit.

- (iii) Following table shows the observations of inputs using the logic probe.

| • | Α        | В        | С     |

|---|----------|----------|-------|

|   | No light | No light | Light |

| 1 | No light | Light    | Blink |

| 1 | light    | ' light  | Blink |

Indicate the corresponding observations of the logic probe on the output Q for the following faults for each of the above input conditions.

- Fault 1:- D4 short circuited

- Fault 2:- D3 short circuited

- (b) Consider the logic circuit shown in Figure-Q7(b),

- (i) The inputs and the output of the circuit are A, B, C and F respectively. Derive a fault table for stuck-0 and stuck-1 faults at the inputs and the output. The fault table shows the response of the

fault free circuit and the circuit with the faults. You may assume that there is only one fault for one instance.

- (ii) Using the results in (b) (i), derive the minimum number of the input combinations that detects all the faults stated above.

- 8. (a) What is used to match the input impedance of the RF amplifier of a TV to that of an antenna?

- (b) Show in a block diagram how the TV signal is processed after extracting sound in a color receiver.

- (c) What are the signals used to ensure the lines and the frames in their proper places?

- (d) Explain how the detected Y and colour component signals are used to recover the colour signals R, G and B in a PAL receiver.

- (e) How does the receiver colour decoder carrier signal is kept in phase with the transmitter colour encoder carrier signal?

- (f) In a defective TV receiver, sound signal and the raster is received but no picture. What could be the faulty sections? Explain how you are going to locate the fault using an oscilloscope.