## THE OPEN UNIVERSITY OF SRI LANKA DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING BATCHELOR OF TECHNOLOGY-LEVEL 3

FINAL EXAMINATION - 2015/2016

ECX3230 - Electronics

(Closed Book)

Answer any five questions.

Date 20.11.2016

Time: 09:30-12:30 hrs.

- Q1. (a) Using appropriate graphs, briefly describe the behavior of the PN junction in biased and unbiased situations. (4Marks)

- (b) List three special purpose diodes and state an application for each. (3Marks)

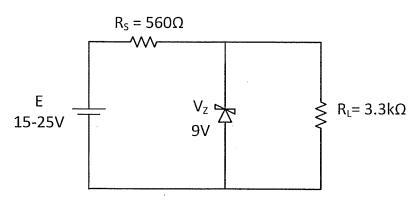

- (c) A voltage stabilizer circuit is shown in Figure Q1. Maximum power dissipation of the Zenner diode is 0.25W.

Figure Q1

- i. The battery is set to 15V. Calculate the currents through the load and the Zenner diode. (2marks)

- ii. Recalculate the currents through the load and the Zenner diode if the battery voltage is set to 25V. (1marks

- iii. Calculate the load dissipation when the Zenner diode is operating in maximum dissipation. (4marks)

- iv. Explain a modification that you suggest to operate a load that consumes about 1A. (6marks)

[Hint: You may add an active device for the modification without changing the specifications of the given circuit.]

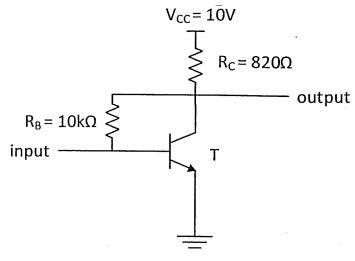

Q2. A common emitter BJT transistor amplifier is shown in Figure Q2 where the Si transistor D55

## (T) has a current gain of 50.

Figure Q2

| (a) Draw the DC load line.                                                      | (4Marks) |

|---------------------------------------------------------------------------------|----------|

| (b) Find the base current at the Q point.                                       | (4Marks) |

| (c) Mark the Q point on the load line.                                          | (2Marks) |

| (d) What is the maximum amplitude value of the undistorted output signal?       | (4Marks) |

| (e) Derive an expression for the stability factor for the circuit in Figure Q2. | (4Marks) |

| (f) Hence calculate the stability factor.                                       | (2Marks) |

|                                                                                 |          |

Q3.

- (a) State the De Morgan's theorem for Boolean variables A, B and C. (2Marks)

- (b) Simplify the following logic functions using Boolean algebra.

i.

$$X_1 = (\overline{A} + \overline{B}).(\overline{ABC}).(\overline{\overline{AC}})$$

ii.

$$X_2 = \bar{A}BC + \bar{A}\bar{B}C + \bar{A}B\bar{C} + ABC + AB\bar{C}$$

(2x3Marks)

(c) The input to a combinational logic circuit is a 4 bit binary number ABCD. Here D is the least significant bit. The output of the circuit will be high when the input satisfies the following conditions;

Odd numbers that are greater than 2 and the remainder is not equal to 1 when divided by 5

Or

Number that are greater than 9 and should not be divisible by 3.

- i. Draw the truth table and the Karnaugh map for the output function (6Marks)

- ii. Minimize the logic function for the output using Karnaugh map and implement it using 2 input NAND gates. (6Marks)

00058

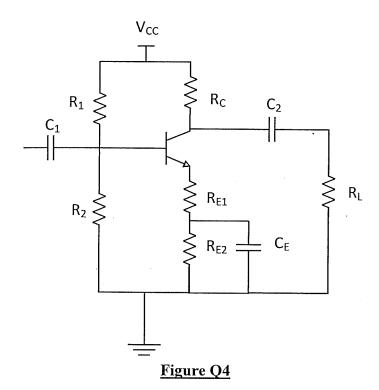

Q4. A small signal amplifier circuit is shown in Figure Q4. Forward current gain and the input impedance are 50 and  $1k\Omega$  respectively and neglect the effect of the  $h_{oe}$  and  $h_{re}$  of the h parameter model.

- (a) Draw the AC h parameter equivalent circuit for the amplifier in Figure Q4.(5Marks)

- (b) Using above parameters, derive the expressions for the following.

| 1.   | Current gain     | (3marks) |

|------|------------------|----------|

| ii.  | Voltage gain     | (3marks) |

| iii. | Power gain       | (3marks) |

| iv.  | Input impedance  | (3marks) |

| v.   | Output impedance | (3marks) |

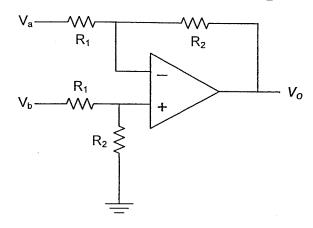

(a) An application of an operational applier is shown in Figure Q5.

Figure Q5

- i. Derive an expression for the output of the circuit shown in Figure Q5. (4Marks)

- ii. What is the function of this circuit?

(2Marks)

- iii. If  $V_a = 5 \sin 1000t$  and  $V_b = 10 \sin 1000t$  and  $R_1 = R_2 = 1k\Omega$ , draw the output of the circuit. (4Marks)

- (b) Write short notes on the following.

(2x5Marks)

- i. UJT

- ii. N channel JFET

Q6.

(a) Draw the V-I characteristics of a Thyristor.

(4Marks)

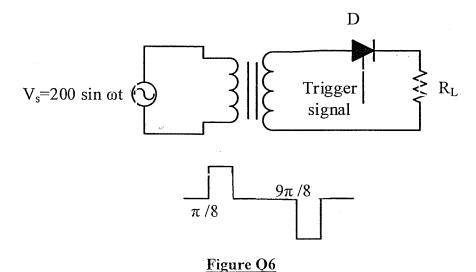

(b) A half wave rectifier circuit is shown in Figure Q6.

i. Draw the waveform across the load R<sub>L</sub>.

(5Marks)

ii. If the triggering signal is applied at  $\frac{\pi}{2}$  of the signal input, what will happen to the power of the load?

(3Marks)

- (c) The circuit current of a RLC circuit is 3mA. Voltage across the inductor and the capacitor are 30V and 18V respectively. The resistance of the resistor is  $1000\Omega$ .

- i. What is the supply voltage to the RC circuit?

(3Marks)

- ii. Derive an expression for the oscillation of the circuit and calculate the oscillating frequency. (5Marks)

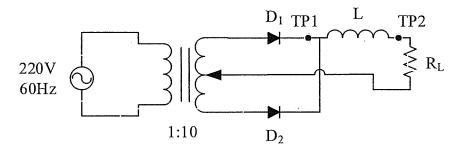

- Q7. A power supply unit is shown in Figure Q7.

Figure Q7

- (a) Write the type of rectification in this circuit in Figure Q7. (2Marks)

- (b) Draw the signal at TP1 and TP2.

(6Marks)

- (c) Derive an expression for the ripple factor of the filter given in the circuit. (6Marks)

- (d) Design a regulator circuit to improve the regulation of this circuit. (You have to calculate the component values) (6Marks)

Q8.

Design a counter circuit which counts 1 to 7.

(a) How many flip flops are required to design this counter?

(b) Draw the state diagram for the counter.

(c) Draw the truth table and the state transition table.

(d) Simplify the functions using Karnaugh maps.

(e) Design the circuit with required components.

(1Marks)

(6Marks)

(6Marks)

(6Marks)

(6Marks)