The Open University of Sri Lanka

B. Sc. Degree program - Level 04

Final Examination 2007

CSU 2178: Digital Computer Fundamentals

Duration: Two and half hours  $(2^{1}/2)$

Date: 20.06.2007

Time: 1.30 pm- 4.00 pm

Answer **FOUR** Questions ONLY.

Q1.

- a. Briefly describe the following

- i. Master control block

- ii. Direct memory access

- iii. Magnetic tapes

- b. Discuss the advantages and disadvantages of using cache memory.

- c. Using D type flip -flop and suitable logic gates, show how to construct a RAM cell with read write and select facilities.

- d. Create four-word by eight bit RAM by using two four-word by four-bit RAMs.

Q2.

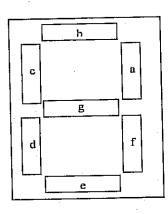

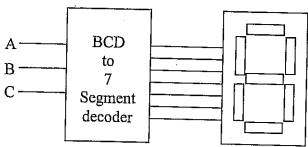

- a. Following table shows truth table of the BCD-to-7 Segment decoder.

- i. Complete the following truth table.

|   | value |   |   | 7-segment display |   |   |   |   |   |  |

|---|-------|---|---|-------------------|---|---|---|---|---|--|

| A | В     | C | a | b                 | С | d | е | f | g |  |

| 0 | 0     | 0 | 1 | 1                 | 1 | 1 | 1 | 1 | 0 |  |

| 0 | 0     | 1 | 1 | 0                 | 0 | 0 | 0 | 1 | 0 |  |

| 0 | 1     | 0 |   |                   |   |   |   |   |   |  |

| 0 | 1     | 1 |   |                   |   |   |   |   |   |  |

| 1 | 0     | 0 |   |                   |   |   |   |   |   |  |

| 1 | 0     | 1 |   |                   |   |   |   |   |   |  |

| 1 | 1     | 0 |   | 1                 |   |   |   |   |   |  |

| 1 | 1     | 1 |   |                   |   |   |   |   |   |  |

ii. Design a circuit for any three values of BCD-to-7 Segment decoder.

- b. International Cricket Council (ICC) wants to develop special type of score board to display scores in the forthcoming World Cup cricket matches. A batsman can score 0 7 for a single ball. Assume that you have seven segments Display, BCD to 7-segment decoder and seven switches.

- i. Create a truth table for a circuit diagram to implement this.

- ii. Design the circuit diagram.

It will clear if the block diagram includes the circuit to be designed and the seven switches.

Q3.

a. Using truth tables show that

i.

$$A+B+C = (A+B) + C$$

ii.

$$A + \overline{A} = 1$$

iii.

$$A.1 = A$$

iv.

$$\overline{A} \cdot \overline{B} = \overline{(A+B)}$$

b. Using Boolean algebra and show that

i.

$$\overline{A}.\overline{B}.\overline{C}.\overline{D} + \overline{C}.\overline{A}.D + \overline{C}.\overline{A}.B = \overline{A}.\overline{C}$$

ii. A.B.C.D +

$$\overline{C}$$

.D.B +  $\overline{A}$ .B.D = B.D

c. A Nuclear power controlling system contains four sensors to monitor temperature (A), pressure (B), Density (C) and Boron plates (D). Each A,B,C and D values represent high as '1' and low as '0'. Function of the controlling system as follows.

$$F = \overline{A} \cdot \overline{B} \cdot \overline{C} \cdot \overline{D} + \overline{C} \cdot D + A \cdot B \cdot C \cdot D + \overline{A} \cdot B$$

- i. Using Boolean algebra and K-Map show that,  $F = \overline{A} \cdot \overline{C} + B \cdot D + \overline{C} \cdot D + \overline{A} \cdot B$ .

- ii. Implement above circuit using basic gates.

- a. Briefly describe the following

- i. Radix Number System

- ii. The EBCDIC character set

- iii. Unicode character set

- b. Convert following binary numbers into octal and hexadecimal

- i. 101011001010<sub>2</sub>

- ii. 1000100.011<sub>2</sub>

- c. Use Two's complement addition to perform the following calculation

- i.  $12_{10} + 33_{10}$

- ii. 20<sub>10</sub> 27<sub>10</sub>

- d. Design a truth table for full adder.

- e. Implement Full Adder using basic logic gates.

Q5.

- a. Briefly describe the following using suitable truth tables and Circuit diagrams

- i. S-R Flip-flop

- ii. J-K Flip-flop

- b. Develop a four-bit register using J-K flip flops

- c. What are the differences between synchronous and asynchronous counters

- d. Draw 4 bit up counter and a down counter.

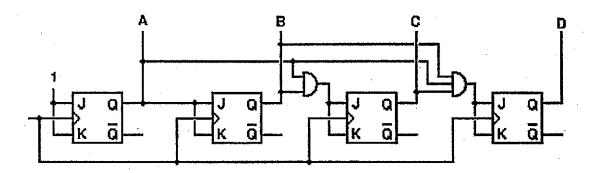

- e. Explain the counter circuit given bellow.

## Q6.

- a. Briefly describe the following using suitable truth tables and circuit diagrams

i. 4-to-1 Multiplexer

- ii. Decoders

- b. Design 8-to-1 Multiplexer using two 4-to-1 Multiplexers

- c. Implement AND gate, an OR gate and a XOR gate using NAND gates.

- d. Find the minimal logic expression for the following truth table using the K-MAP method. Design a circuit to implement this truth table using 3-input NAND gates only.

| A             | В  | C   | D | F                     |

|---------------|----|-----|---|-----------------------|

| <b>A</b> 0    | 0  | 0   | 0 | 1                     |

| 0             | 0  | 0   | 1 | 1<br>1<br>0           |

| 0             |    | 1   | 0 | 0                     |

| 0             | 0  | 1   |   | 0                     |

| 0             | 1  | 0   | 0 | 0                     |

| 0             | 1_ | 0   | 1 | 1<br>X<br>0<br>1<br>0 |

| 0             | 1  | 1   | 0 | X                     |

| 0             | 1  | 0 0 | 1 | 0                     |

| 1             | 0  | 0   | 0 | 1                     |

| 1             | 0  |     | 1 | 0                     |

| $\frac{1}{1}$ | 0. | 1   | 0 | 1                     |

| 1             | 0  | 0   | 1 | 0                     |

| 1             | 1  | 0   | 0 | 0                     |

| 1             | 1  | 0   | 1 | 1                     |

| 1             | 1  | 1   | 0 | 0                     |

| 1             | 1  | 1   | 1 | 1                     |

\*\*\* All right reserved \*\*\*