THE OPEN UNIVERSITY OF SRI LANKA FACULTY OF NATURAL SCIENCES

B. SC. DEGREE PROGRAMME 2012/2013

DEPARTMENT OF PHYSICS

FINAL EXAMNINATION DURATION: - 3 HOURS

### **PYU2262- ELECTRONICS**

DATE:- 14-12-2013

FROM 1.30 P.M. TO 4.30 P.M.

### ANSWER 06 QUESTIONS ONLY, INCLUDING QUESTION No. 01 IN PART A

(Question No. 01 is compulsory)

#### PART A

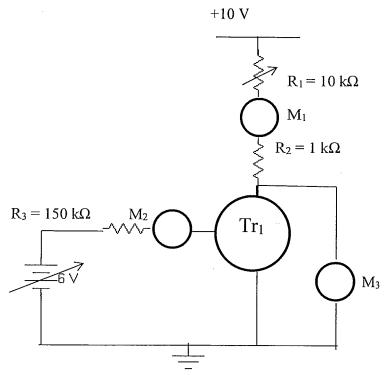

1. Figure shows a sketch diagram of the circuit to measure the output of a transistor

- i. Redraw the circuit diagram with a suitable transistor

- ii. List the apparatus and components that you may use in this experiment.

- iii. Describe the type of the transistor that you may use in this experiment with reasons.

- iv. Identify the meters M1, M2 and M3 used in this circuit.

- v. Write down the initial adjustment that you may do in this experiment.

- vi. Describe the function of the variable resistor R<sub>1</sub>.

- vii. Write down the steps that you may follow to take readings from M1 and M3?

- viii. Write down the steps that you may make in order to identify the operating point.

- ix. Sketch the expected output characteristics of the transistor with labeling the relevant axises.

# PART B (ANSWER ANY 05 QUESTIONS FROM PART B)

- 1. a. (i) Write down advantages of semiconductor device in electronic industries.

- (ii) If a student claims that "An extrinsic semiconductors contains equal numbers of electrons and holes" discuss this statement.

- (iii) Discuss the differences between the Light Emitting Diode (LED) and Photo Diode

- (iv) Explain changes occurs in the depletion region when the PN junction is in

- (a) forward biased

- (b) Reverse biased

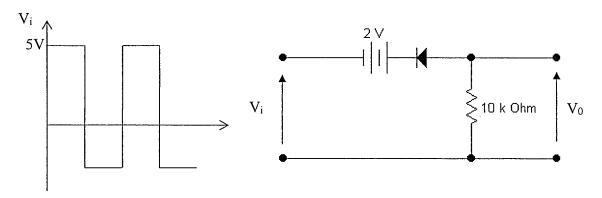

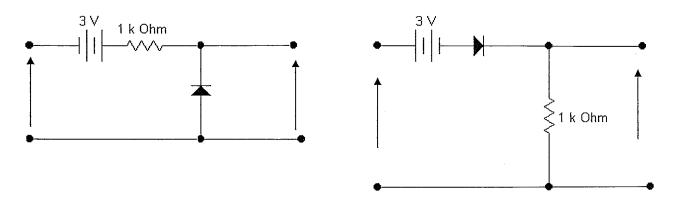

- b. Plot output wave form  $(V_o)$  for the circuit in the following figure for the input  $(V_i)$  shown. Assume that forward voltage of the given diode is 0.7 V.

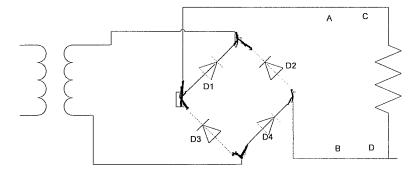

- 2. a. Figure shows an incorrect full wave bridge rectifier circuit drawn by a student.

- (i) Redraw the correct circuit diagram in your answer sheet.

- (ii) Draw the smoothing capacitor in the correct position of your circuit diagram in order to get the smoothed output wave form.

- (iii) Sketch the variation of the output wave forms for different capacitor values one high and one low.

- (iv) Output wave of the transformer is  $V_m \sin 2\pi f t$  where  $V_m$  is peak voltage and f-frequency of the wave

Show that dc value of the output voltage  $(V_{dc})$  is given by

$$V_{dc} = \frac{2V_m}{\pi}$$

- (v) If you are given a zener diode having  $V_Z=9$  V, modify and redraw the given circuit to obtain a regulated voltage supply.

- b. i. What do you understand by a Clipper circuit and a Clamper Circuit?

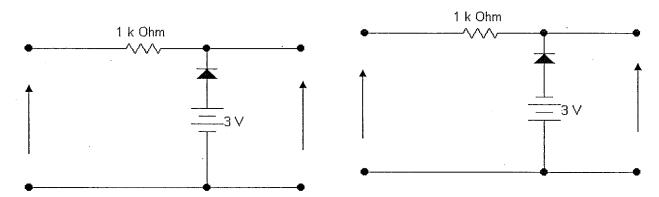

- ii. Draw the output wave form for the following circuit diagrams when the input wave form is sinusoidal with  $V_m = 10 \text{ V}$ .

iii. Draw the output wave form for the following clamping circuits when the input wave form is a sinusoidal with  $V_m = 10 \text{ V}$ .

- 3. a. Define the hybrid parameters  $h_{fe}$  and  $h_{ie}$  for a basic transistor circuit in CE configuration.

- ii. Voltage gain  $(A_V)$  of a transistor amplifier is given by the following expression.

$$A_V = -\frac{h_f R_L}{(1 + h_o R_L) h_i}$$

When  $\frac{1}{h_o} \gg R_L$  show that for practical purposes the above expression can be reduced to  $-\frac{h_{fR_L}}{h_i}$  (Here Symbols have their usual meanings)

- b. A CE configuration transistor amplifier with self-bias or voltage-divider bias is required to have a voltage gain of about -200. An *npn* silicon transistor with  $h_{fe} = 100$ ,  $h_{ie} = 1 \text{ k}\Omega$  and maximum collector power dissipation of 75 mW is available. (Neglecting  $h_{re}$  and  $h_{oe}$  and using  $V_{CC} = 12 \text{ V}$ )

- i. Draw the circuit diagram with  $R_1$ ,  $R_2$ ,  $R_L$  and  $R_E$  (Here Symbols have their usual meanings)

- ii. Find the value of  $R_L$

- Determine the current  $I_C$  through  $R_L$  assume that  $V_{CG} = V_{CC}/2$  where G is the ground terminal.

- iv. Assuming power dissipation of the collector and emitter (CE) junction as 15 mW. Show that  $V_{EG} = 1.2 \text{ V}$ , hence find the  $R_E$

- 4. a. i. Discuss the fundamental differences among class A, class B and class C amplifiers

- ii. Discuss the differences between the parallel and series tuned circuits

- iii. What is a tuned amplifier?

- iv. Explain with a circuit diagram the operation of a single-tuned amplifier

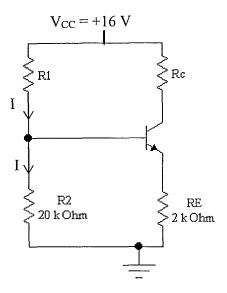

- b. An *npn* transistor circuit given below has  $\alpha=0.985$  and  $V_{BE}=0.3$  V. and  $R_2=20$  k $\Omega$ ,  $R_E=2$  k $\Omega$  and VCC =16 V. Answer the following questions placing Q point at  $I_C=2$  mA and  $V_{CE}=6$  V

- i. Determine the current gain  $\beta$

- ii. Show that the voltage across R<sub>2</sub> is 4.3 V

- iii. Determine the  $R_C$  and  $R_1$  assuming current passing through  $R_1$  and  $R_2$  are same.

- 5. a. i. Discuss the concept of feedback in amplifiers with a proper diagram.

- ii. Explain what do you understand by the positive and negative feedback

- iii. To an amplifier without a feedback circuit, if you introduce a negative feedback what changes you will obtain in the output of the amplifier.

- iv. Show that the output impedance  $(R_{of})$  of the feedback amplifier circuit can be written as  $R_{of} = \frac{R_o}{1 A_V \beta}$  Where  $R_o$ -output impedance without feedback,  $A_V$  Voltage gain without feedback,  $\beta$  feedback factor

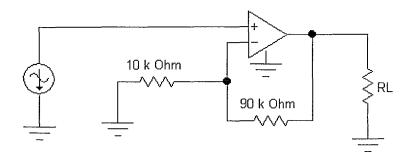

- v. Figure shows the circuit of a negative voltage feedback amplifier. If without feedback, Voltage gain  $A_V = 10{,}000$ , input impedance  $R_i = 10 \text{ k}\Omega$  and output impedance  $R_o = 100 \Omega$ , Determine

- a. the feedback fraction  $(\beta)$

- b. gain with feedback  $(A_{\nu f})$

- c. the output impedance with feedback ( $R_{0f}$ )

- 6. a. i. Determine the binary equivalent of 13.875

- ii. Find the decimal equivalent of 101.1101

- iii. Determine the binary equivalent of the hexadecimal number A5D

- iv. Find the hexadecimal equivalent for the decimal number of 581

- v. Perform the binary addition 11000.11 + 101.111

- b. Prove the following expressions using Boolean Algebra

i.

$$ABC + A\overline{B}C + AB\overline{C} = A(B+C)$$

ii.

$$(A+B)(A+C) = A+BC$$

iii.

$$(A+B)(A+\bar{B})(\bar{A}+C) = AC$$

iv.

$$(\bar{A} + B)(A + B) = B$$

c. Find the complement  $(\overline{Y})$  of the expressions given below

i.

$$Y = AB\overline{C} + A\overline{BC}$$

ii.

$$Y = \overline{A} + (B\overline{C} + \overline{B}C)$$

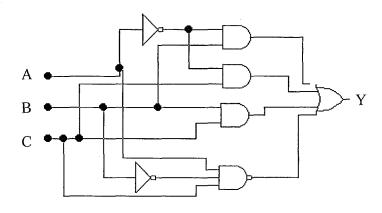

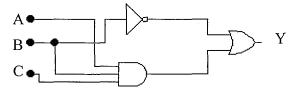

- 7. a. Obtain the Boolean expressions for the output Y in the logic circuits given below.

- ii. Simplify the Boolean expressions that you have written in part (i)

- iii. Draw the logic circuit diagrams for the simplified Boolean expressions.

Circuit diagram 1

# Circuit diagram 2

b. Simply the following function by using K map method.

i.

$$X = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C + AB\overline{C}$$

ii.

$$X = \overline{A}BC + A\overline{B}C + AB\overline{C} + ABC$$

iii.

$$X = \overline{ABC} + \overline{ABC} + A\overline{BC} + AB\overline{C}$$

iv.

$$X = \overline{ABC} + \overline{ABC} + A\overline{BC} + ABC$$

- c. A burglar alarm should be activated when the two conditions given below are simultaneously satisfied

- (a) The main entrance door of the building is open, and

- (b) The bed room door and /or the kitchen door is open.

Write the truth table and construct the logic expression to operate the alarm using one AND gate and one OR gate.

- 8. a. How is an RS flip-flop converted into a JK flip-flop? Give its truth table and explain how it is obtained

- b. Explain use of preset and clear inputs in a flip-flop

- c. What is a De-multiplexer? How can a decoder circuit be used as a De-multiplexer? Give the block diagram of a 4-to-16 line De-multiplexer