## THE OPEN UNIVERSITY OF SRI LANKA DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING BATCHELOR OF TECHNOLOGY

FINAL EXAMINATION - 2014/2015

## ECX6250 - ANALOG ELECTRONIC SYSTEMS

(Closed Book)

## ANSWER ANY FIVE QUESTIONS.

Date 16.09.2015

Time: 9:30-12:30 hrs.

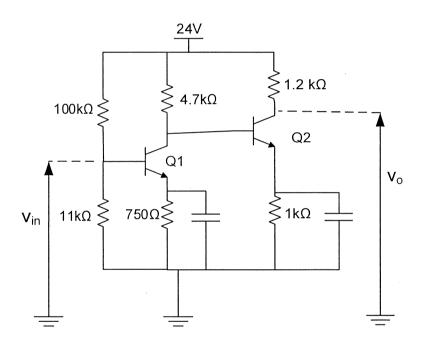

Q1. Consider the circuit in the Figure-Q1 with Si transistors.

Figure-Q1

Q1:

$$\beta = h_{fe} = 100, h_{ie} = 1k\Omega$$

Q2:

$$\beta = h_{fe} = 60, h_{ie} = 1.4k\Omega$$

You may assume that the effect from  $h_{oe}$  and  $h_{re}$  are negligible.

(a) Find the quiescent values of  $V_{CE1}$ ,  $I_{C2}$ ,  $V_{C2}$  and  $V_{CE2}$ . (8 Marks)

(b) Draw the low frequency equivalent circuit. (6 Marks)

(c) Find the mid band voltage gain  $\frac{V_o}{V_{in}}$ . (6 Marks)

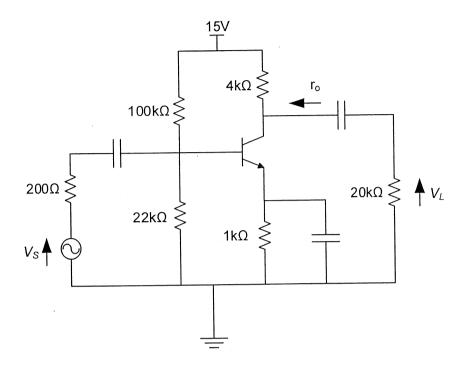

Q2. The transistor in Figure-Q2 has the a low frequency  $\beta$  of 120,  $r_e = 20\Omega$  and  $r_o = 100k~\Omega$ . The inter-electrode capacitances are  $C_{be} = 40pF$ ,  $C_{bc} = 1.5pF$  and  $C_{ce} = 5pF$ . There is a wiring capacitance equal to 4pF across the input and 8pF across the output.

Figure-Q2

- (a) Draw the high frequency equivalent circuit for this amplifier circuit. (6 Marks)

- (b) Calculate the input and output impedances. (8 Marks)

- (c) Hence, find the approximate upper cutoff frequency of this amplifier. (6 Marks)

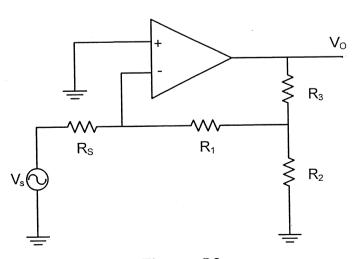

Q3.

Figure -Q3

Consider the feed-back arrangement in the above Figure-Q3 circuit diagram. Let the open loop gain of the op-amp is 10,000 and the source input resistance is  $100k\Omega$ .

$$R_1 = R_3 = R_S = 1k\Omega, \ R_2 = 100k\Omega.$$

a) Identify the type of feed-back used.

(2 Marks)

- b) Calculate the feedback factor, considering the effect of the input resistance. (8 Marks)

- c) Let the amplifier is connected with a load  $R_L = 1k\Omega$ . Calculate the total closed-loop gain considering the effects of load and input resistances. (10Marks)

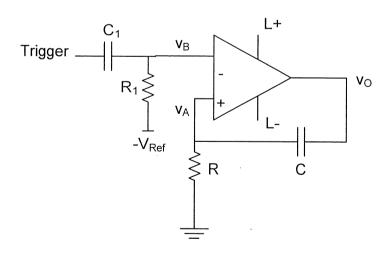

Q4.

- (a) Draw the transfer characteristic curves for ideal and non-ideal comparators and compare them. (4Marks)

- (b) The one shot circuit shown in Figure-Q4 is having  $v_0 = L +$ ,  $v_A = 0$  and  $v_B = -V_{Ref}$  in the stable state. The circuit is triggered by applying a positive input pulse greater than  $V_{Ref}$ . Assume that  $R_1C_1 \ll RC$ .

- i. Sketch the waveforms of  $v_A$  and  $v_O$  along with the trigger pulse. (4Marks)

- ii. What is the width of the pulse (T) generated at the output? (4Marks)

- iii. Explain how T can be controlled. (3Marks)

Figure-Q4

(c) Draw the circuit diagram of a free running square wave generator using a Schmitt trigger circuit. (5Marks)

- Q5. (a) Starting from the first principles derive the Barkhausen criterion for the oscillations to occur. (4 Marks)

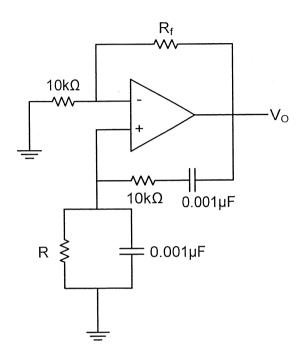

- (b) The circuit diagram of a Wien-Bridge oscillator is shown in Figure-Q5. Calculate,

- i. The range of R variation required to obtain oscillations in the range of 10kHz 50kHz. (10 Marks)

- ii.  $R_f$  value required for oscillations to occur at 10kHz. (6 Marks)

Figure –Q5

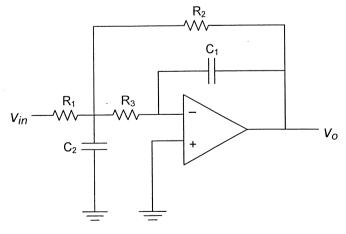

Q6.

(a) List output characteristics of three commonly used active filters Butterworth, Elliptic and Chebyshev. (6 Marks)

Figure-Q6

- (b) A second order filter stage is shown in figure-Q6.

- i. Show that the transfer function is given by

$$A(s) = -\frac{\frac{R_2}{R_1}}{1 + C_1(R_2 + R_3 + \frac{R_2R_3}{R_1})s + C_1C_2R_2R_3s^2}.$$

(7 Marks)

ii. Use the second order stage in figure-Q6 and other circuitry as necessary to design a third-order unity gain Butterworth low-pass filter with a cutoff frequency  $f_C = 50kHz$ . (7Marks)

Note: Butterworth coefficients of the third order filter are.

| Order n | Stage i | $a_i$ | $b_i$ |

|---------|---------|-------|-------|

| 3       | 1       | 1     | 0     |

|         | 2       | 1     | 1     |

for a transfer function of a stage of the form,

$$A_{i(s)} = \frac{A_0}{1 + a_i s + b_i s^2}.$$

Q7.

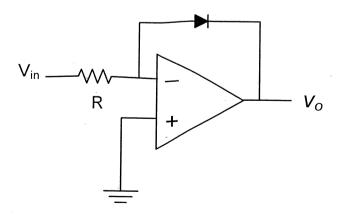

- (a) Starting from the diode characteristic equation  $I_D = I_S \left( e^{\frac{V_D}{\eta V_T}} 1 \right)$  derive an expression for the intrinsic resistance,  $r_e$  of the diode junction. (4 Marks)

- (b) Figure-Q7 (b) shows a diode-based log amplifier. Show that  $V_o \propto \ln(V_{in})$ . (8 Marks)

Figure-Q7 (b)

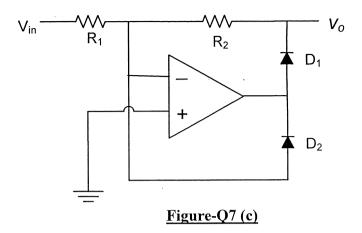

(c) Explain the operation of the precision rectifier arrangement shown in Fig-Q7 (c). (8 Marks)

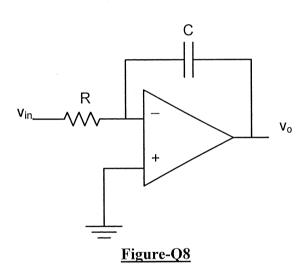

Q8.

- (a) Assuming an ideal operational amplifier except a finite gain, derive the voltage gain transfer function of the above circuit in Figure-Q8. (4Marks)

- (b) Hence, sketch the magnitude and phase Bode plots. Plot the magnitude and phase Bode plots for an all ideal operational amplifier in the same sketch. (Clear axis labeling and plots are required. Assume  $R = 1.6k\Omega$  and  $C = 0.01\mu F$ ) (8Marks)

- (c) If this operational amplifier is a real dominant pole amplifier with a low frequency gain of 60dB and a pole at 100Hz, determine the usable frequency range of the above circuit. (8Márks)